Site Search

Contact: Mr Yuan

Mobile:18822809251

Tel:+86-0755-2314670

QQ:2144782477

e-mail:szhsxpcb@126.com

Address:No. 1 Xinhe Avenue, 8th Industrial Zone, Gonghe Community, Shajing Sub-District Office, Bao'an District, Shenzhen .

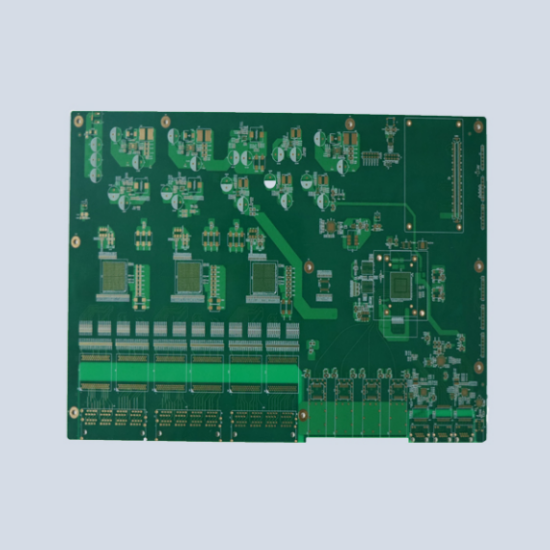

Production Process and Prototyping Challenges of Multilayer PCBs

The production of circuit boards currently mainly employs the subtractive method, where excess copper foil on the raw material (copper-clad laminate) is removed to form the conductive pattern.

Production Process of Multilayer PCBs (Subtractive Method)

The subtractive method mostly relies on chemical etching, which is both economical and efficient. However, chemical etching attacks indiscriminately, so the desired conductive pattern needs to be protected by coating it with a layer of etch resist. The unprotected copper foil is then etched away. In the early days, etch resist was applied in the form of ink using screen printing, hence the term "printed circuit board (PCB)". However, as electronic products have become increasingly sophisticated, the image resolution of printed circuits can no longer meet product requirements, leading to the adoption of photoresist as the image resolution material. Photoresist is a photosensitive material that reacts to light of a certain wavelength, undergoing a photochemical reaction to form a polymer. By selectively exposing the pattern using a photographic negative and then developing it with a solution (e.g., 1% sodium carbonate), the unpolymerized photoresist is removed, leaving the pattern protected.

Interlayer connectivity is achieved through plated-through holes. Therefore, drilling and plating of the holes are necessary steps in the PCB production process to achieve interlayer connectivity.

Taking a conventional six-layer PCB as an example, the production process is as follows:

Produce two double-sided boards without holes

Cutting (raw material: double-sided copper-clad laminate) - Inner layer pattern creation (forming the etch resist layer) - Inner layer etching (removing excess copper foil)

Bond the two prepared inner layer cores with epoxy resin glass fiber prepreg

The two inner layer cores are riveted with the prepreg, and a copper foil is laid on each outer surface. The assembly is then pressed under high temperature and high pressure to achieve bonding. The key material is the prepreg, which has the same composition as the raw material (epoxy resin glass fiber) but is in a partially cured state. It liquefies at 70-80°C and contains a curing agent that crosslinks and cures with the resin at 150°C, becoming irreversible. Through this transition from semi-solid to liquid to solid state, bonding is achieved under high pressure.

Multilayer PCBs are more complex than single or double-sided boards in terms of both design and manufacturing. Care must be taken to avoid potential issues. What challenges should we avoid in the prototyping of multilayer PCBs?

Challenges in Prototyping Multilayer Impedance Boards

Challenge of Layer-to-Layer Alignment

Due to the numerous layers in multilayer PCBs, users have increasingly high requirements for layer alignment. Typically, the alignment tolerance between layers is controlled within 75 micrometers. Considering factors such as the large unit size of multilayer PCBs, variations in temperature and humidity in the graphic transfer workshop, misalignment caused by inconsistencies between different core boards, and layer-to-layer positioning methods, controlling alignment in multilayer PCBs is more difficult.

Challenge of Inner Circuit Fabrication

Multilayer PCBs use special materials such as high-TG, high-speed, high-frequency, thick copper, and thin dielectric layers, which impose high requirements on inner circuit fabrication and graphic dimension control. For example, the integrity of impedance signal transmission increases the difficulty of inner circuit fabrication. Small width and line spacing lead to increased open and short circuits, resulting in low yield rates. With multiple fine-line signal layers, the probability of AOI (Automated Optical Inspection) missing defects in inner layers increases. Thin inner core boards are prone to wrinkling, poor exposure, and curling during etching. High-layer boards are often system boards with large unit sizes, and the cost of product scrap is high.

Challenge of Lamination Manufacturing

With multiple inner core boards and prepregs stacked together, defects such as slippage, delamination, resin voids, and bubble residue can easily occur during lamination. In the design of the lamination structure, factors such as material heat resistance, pressure resistance, resin content, and dielectric thickness should be fully considered to formulate a reasonable lamination plan for multilayer PCBs. Due to the multiple layers, it is difficult to maintain consistency in expansion and contraction control and dimensional coefficient compensation, and thin interlayer insulating layers can easily lead to failures in interlayer reliability tests.

Challenge of Drilling

The use of special materials such as high-TG, high-speed, high-frequency, and thick copper increases the difficulty of achieving low drilling roughness, reducing drilling burrs, and removing drill smear. With multiple layers and increased total copper thickness and board thickness, drilling is prone to tool breakage. Dense BGAs and narrow hole wall spacing can lead to CAF (Conductive Anodic Filament) failure issues. The thickness of the board can easily cause drill skew problems.

+8618822809251

Website:www.huashing-pcb.com

Address:No. 1 Xinhe Avenue, 8th Industrial Zone, Gonghe Community, Shajing Sub-District Office, Bao'an District, Shenzhen .